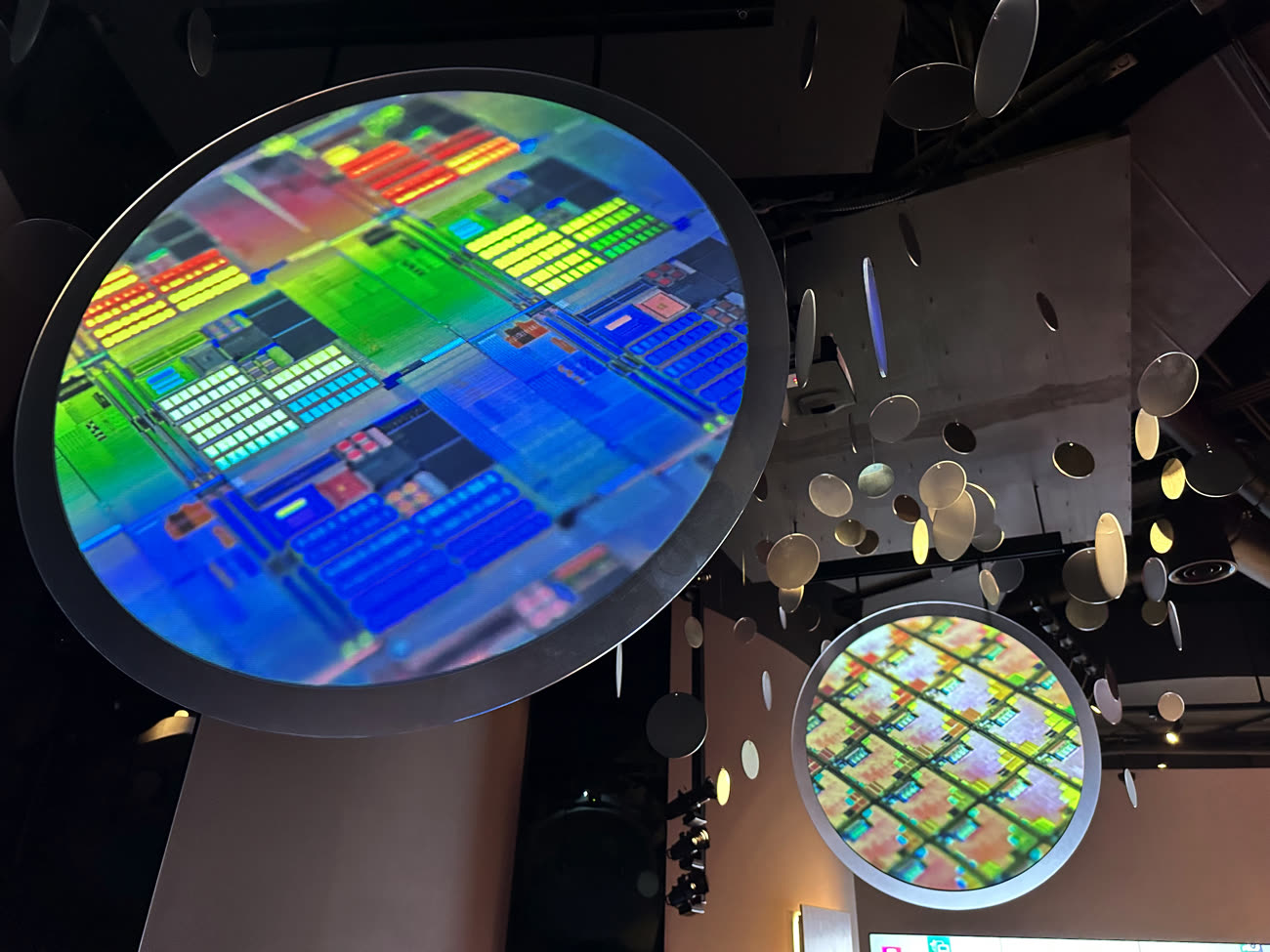

TSMC, le fondeur taïwanais, a donné quelques informations sur ses prochaines technologies, avec des détails sur les différentes versions du 3 nm mais aussi sur l'étape suivante, le 2 nm, qui est attendue en 2025 dans le meilleur des cas.

Plusieurs variantes du 3 nm

Le processus en 3 nm « standard » porte le nom de N3B, c'est celui qui est a priori employé pour les puces des futurs iPhone et probablement pour l'Apple M3. Il est en production actuellement, et c'est le processus de base. Le second processus 3 nm porte le nom de N3E. C'est une version « low cost » qui possède quelques défauts mais aussi quelques avantages, et elle est attendue au second semestre 2023.

TSMC parviendra-t-il à produire suffisamment de puces à 3 nm en 2023 pour les Mac ?

Le N3E se place entre le N5 et le N3B pour la densité : alors que le 3 nm est 1,7 x plus petit que le 5 nm, le N3E n'est que 1,6 x plus compact. La taille des cellules SRAM, elle, reste d'ailleurs la même qu'en 5 nm. Par contre, TSMC indique que les gains en consommation sont plus élevés que le 3 nm standard (entre 25 et 30 % de baisse par rapport au 5 nm pour le N3B, 32 % pour le N3E). Dans les faits, ce processus n'est donc pas adapté à tous les usages. Prenons le cas d'un processeur : deux méthodes existent pour passer d'un processus à un autre : soit effectuer un die shrink, c'est-à-dire essentiellement réduire la taille de la puce sans rien changer, soit profiter de la nouvelle gravure pour ajouter des fonctions ou de la mémoire cache.

Le N3E est bien adapté au premier cas : il permet de réduire la consommation (à fréquence identique) ou d'augmenter la fréquence (à consommation identique) sans trop changer la puce. Par contre, la limitation sur les puces SRAM réduit l'intérêt de l'augmentation de la mémoire cache, justement composée de cellules SRAM.

Un N3P et un N3X plus performants

Le N3P, attendu au second semestre 2024, va être une amélioration du N3E, avec quelques gains sur la consommation mais surtout une compatibilité directe avec le N3E. Selon le fondeur, une puce pensée pour le N3E pourra ensuite être produite en N3P plus tard sans modifications majeures. On peut le comparer au « 4 nm » actuel, dans un sens. Le dernier, le N3X, vise plutôt les composants qui ciblent les performances, comme certains processeurs. La consommation sera plus élevée que le N3P, mais les performances seront meilleures grâce — notamment — à une plus grande marge sur les tensions. Attendu en 2025, il sera donc adapté aux puces denses et rapides dans lesquelles la consommation n'est pas une contrainte, par exemple les GPU modernes.

Le 2 nm pour la suite

Le 2 nm (N2) va remplacer les transistors FinFet par du GAAFET (gate-all-around, ce que TSMC nomme Nanosheet). Cette structure, pour résumer, permet de réduire les pertes de courant et d'ajuster plus facilement les transistors pour les optimiser pour des performances élevées ou une consommation faible (deux cas antagonistes). Le N2 devrait remplacer le N3E au second semestre 2025 avec des gains classiques : entre 25 et 30 % de réduction sur la consommation et 10 à 15 % d'augmentation des performances.

La suite est évidemment moins détaillée : le N2P est attendu en 2026, avec probablement les premières puces en 2027, comme l'indique Anandtech. Il amènerait un gain en consommation moyen, mais permettrait de réduire la taille des puces de façon importante. Le dernier processus, le N2X, n'a ni date de sortie ni gains annoncés, mais il devrait vraisemblablement équiper les puces performantes de 2028, dans le meilleur des cas. Il n'est par ailleurs pas exclu que TSMC suive la voie d'Intel pour nommer ses futurs processus de gravure : le 2 nm pourrait devenir le 20 Ångströms.

Une histoire de compromis

Terminons par rappeler une chose : dans la majorité des cas, les concepteurs des puces emploient les nouveaux processus pour améliorer l'existant. Le die shrink qui consiste à uniquement réduire la taille d'une puce (et sa consommation) demeure assez rare et les concepteurs préfèrent garder des composants d'une taille à peu près constante en ajoutant des fonctions ou en augmentant les performances.

Dans tous les cas, les différents processus feront probablement partie des keynotes pendant quelques années, pour mettre en avant les avantages des puces Apple.