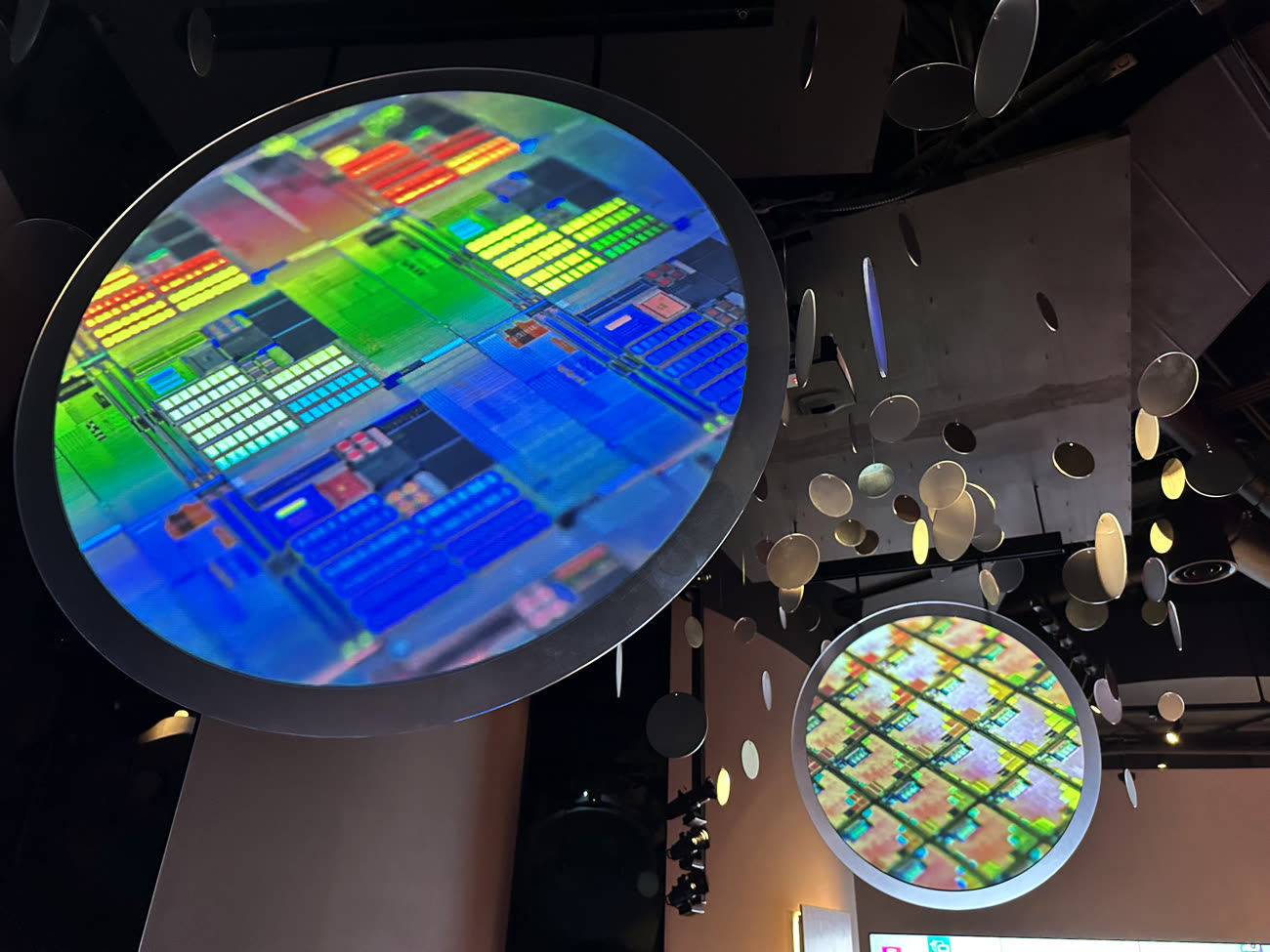

Dans le petit monde de la gravure, la fuite en avant est la norme et les différents grands fondeurs parlent souvent du futur. Et TSMC, leader actuel dans ce domaine, a donné quelques informations sur son procédé en 2 nm, destiné à succéder au 3 nm. 3 nm qui — rappelons-le — n'est pas encore réellement employé même s'il est en production pour Apple depuis plusieurs mois.

N3 : TSMC affine la gravure pour relancer l’innovation

Comme l'explique AnandTech, TSMC va comme à son habitude décliner le 2 nm en au moins deux variantes : le N2 (ou N2B) et le N2P. Le P signifie Performance et c'est le processus employé pour les puces qui doivent monter en fréquence sans forcément de contraintes sur la consommation (par exemple un GPU).

Une des nouveautés, c'est que le N2 classique s'adapte aussi aux puces qui ont besoin d'une fréquence plus élevée tout en gardant une consommation faible, et ce n'est pas paradoxal. Avec le temps, les fabricants doivent produire des puces qui consomment peu dans un usage normal ou faible (sur le bureau avec une carte graphique, en veille avec un smartphone, etc.) mais qui doivent monter rapidement en puissance quand l'utilisateur en a besoin.

Comme souvent, il existe deux voies possibles pour améliorer les puces. La première est le die shrink, c'est-à-dire prendre une puce en 3 nm et la graver en 2 nm, sans modifications particulières sur le fonctionnement. Dans ce cas de figure, TSMC annonce un gain de 25 à 30 % sur la consommation. C'est un choix assez rare, les fabricants de puces préfèrent en réalité la seconde voie : garder une consommation à peu près stable mais augmenter les performances. Dans ce cas, TSMC annonce un gain de 10 à 15 %.

Quelques détails techniques

Une autre nouveauté plus technique est l'utilisation de matériaux avec une résistance plus faible, liée au fait que les transistors deviennent de plus en plus petits. Enfin, TSMC a annoncé un changement dans la façon d'alimenter les puces. Le backside power delivery network (attendu aussi chez Intel et Samsung) consiste à séparer les connexions dédiées à l'alimentation et celles liées aux E/S (entrées/sorties). Avec le N2P, l'énergie peut passer par l'arrière de la puce, ce qui évite une partie des perturbations qu'elle peut provoquer au niveau des E/S. Cette solution permet aussi d'optimiser la taille des fils d'alimentation et in fine d'améliorer l'efficacité énergétique.

Si le 2 nm semble évidemment prometteur, il n'est pas prévu pour tout de suite : la production en masse n'est pas attendue avant la fin de l'année 2025, ce qui implique que les premiers appareils équipés sortiront en 2026 (pour l'iPhone 18 ?). Pour la partie liée à l'alimentation, TSMC annonce une production à la fin de l'année 2026 ou au début de 2027.